I personally got my start in hobby electronics with the big Arduino Uno and ATMega328 family back in the 2010-era.

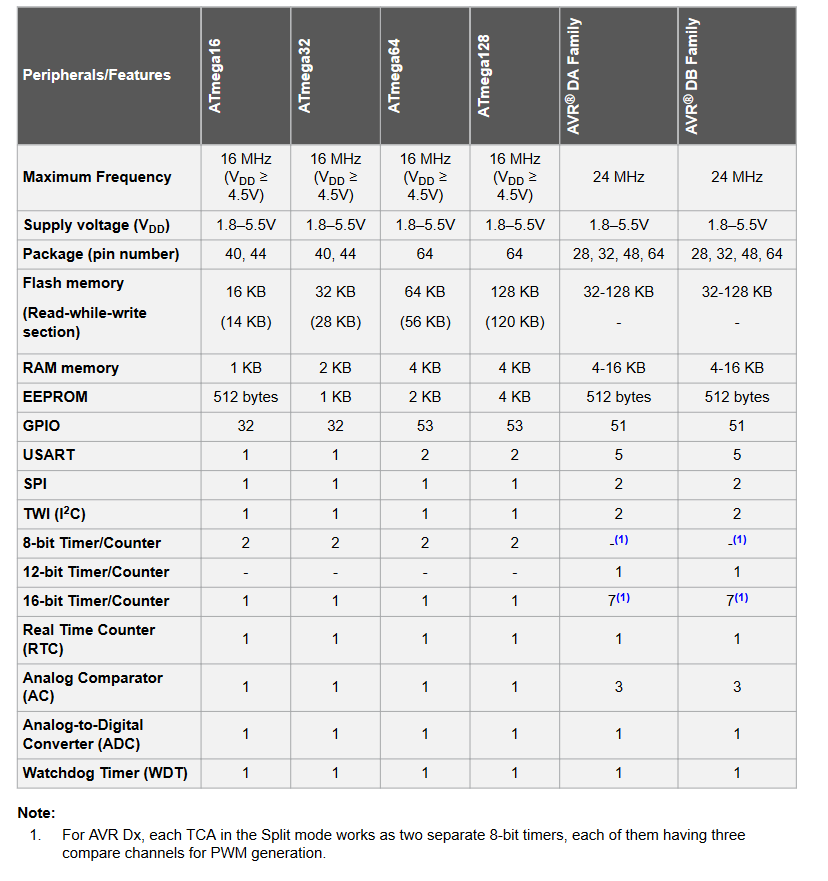

After over a decade of advancements, Microchip has created the AVR DA/DB microcontrollers (as well as DD and EA microcontrollers today). Though these share the same assembly language as the old megaAVR or ATMega328 systems from a decade ago, there are key upgrades (ie: differences) with today’s chips.

This 43-page migration guide helps lay out the differences between the older chips vs the newer chips.

Of particular note is page 4, containing the following summary:

AVR Dx chips seem to have a few faster instructions as well, which means that some assembly-language level timings may differ on today’s chips. Cycle-accuracy is not guaranteed from up-porting, though all results should be the same otherwise.

The biggest selling points IMO are the following:

-

24MHz at all voltage ranges. A modern AVR DD (or DA or DB) can run at 24MHz even at 1.8V. No more consulting the charts for MHz vs Voltage anymore. This also means that modern AVR DD are more power-efficient than the older chips (lower voltage means less current and less power used).

-

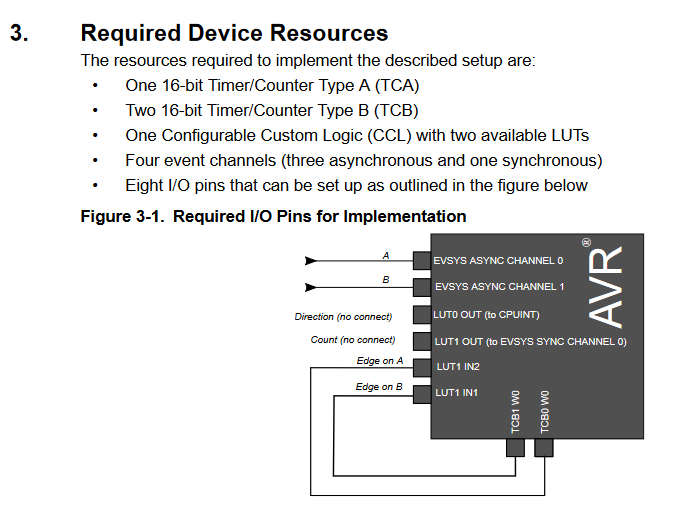

Event System – Modern AVR Dx systems have an internal router system that functions even as the CPU sleeps (depending on sleep state of course). Without getting too far into the details: this means that most modern interrupt sources can set off an “Event”, and that “Event” can be routed as an input-event to most other peripheral.

For example: an input-event to a GPIO (ex: user pushes a button) can be configured as an event instead of an interrupt. The event can be routed to nearly anything, but lets say its routed to TimerB#3. TimerB#3 could be configured as OneShot mode, meaning it will ignore all other events until the timer overflows. TimerB#3 can then trigger an interrupt on overflow.

What I just described is a button debouncer that occurs in parallel to your code, and can occur even when your CPU is a sleep state (and because everything is an “event” instead of an “interrupt”, the CPU remains sleeping throughout this entire process). While interrupts+code is likely simpler to use, the Event System has power-consumption advantages as well as hard latency requirements (ie: often within 100 nanoseconds) that code does not.

- CCL – You have 4x LUTs (lookup tables), much like a mini-FPGA or mini-CPLD on modern AVR chips, that can be driven by the Event system. The CCL is fully integrated into the Event System as both a source and/or a sink of events. There is additionally 2-bits of memory (configured as a D-flipflop, JK-flipflop, D-latch, or RS-flipflop), called “Sequencer Logic” that can participate with the 4x 3-bit LUTs, though the wiring is less flexible than an FPGA/CPLD, its still a welcome feature.

#3 and #2 combine with each other in intricate ways.

By combining #3, #2, and the Timer-system, Microchip has an Application Note for a Quadrature Decoder entirely in CCL + Event Systems + Timers. https://ww1.microchip.com/downloads/en/Appnotes/Interf-Quad-Encoder-CCL-w-TCA-TCB-DS00002434C.pdf

All in all, it seems like Microchip’s “design” of AVRs is to be the master of this… weird… almost FPGA or CPLD-like mini-device.

Its weird and interesting. I think in the face of the modern trend of just offering more SRAM or MHz, its certainly a selling point. Low-latency, low-power glue-logic, flip-flops and timers really don’t need the CPU to get involved (and indeed, keeping the CPU out of it really is a benefit to latency and power anyway).

However, it does seem like a bit of a Devil’s deal. Code, especially code written in C, is often portable. But sticking to Event-sys and this CCL stuff means you’re absolutely, 100% locking yourself into AVR chips for the foreseeable future (or maybe a few SAM-CortexM0+ parts which also have Microchip’s CCL / Eventsys as part of them). Its not like these low-level timer, glue-logic, or timer details will translate very easily to STM32 or TI’s chips after all.

Still, I think CCL + EventSys “just makes sense”. Its obviously a low power, low-latency design available at low costs. And experienced EEs from decades past remember how to use JK FlipFlops or other systems like this (though I wonder how much of that stuff is taught in today’s classes… or if modern college grads would understand how these systems work)